Hudson Institute

JULY 2021

# Regaining the Digital Advantage: A Demand-Focused Strategy for US Microelectronics Competitiveness

BRYAN CLARK AND DAN PATT

CENTER FOR DEFENSE CONCEPTS AND TECHNOLOGY, HUDSON INSTITUTE

© 2021 Hudson Institute, Inc. All rights reserved.

#### **ABOUT HUDSON INSTITUTE**

Hudson Institute is a research organization promoting American leadership and global engagement for a secure, free, and prosperous future.

Founded in 1961 by strategist Herman Kahn, Hudson Institute challenges conventional thinking and helps manage strategic transitions to the future through interdisciplinary studies in defense, international relations, economics, health care, technology, culture, and law.

Hudson seeks to guide public policy makers and global leaders in government and business through a vigorous program of publications, conferences, policy briefings and recommendations.

Visit www.hudson.org for more information.

Hudson Institute 1201 Pennsylvania Avenue, N.W. Fourth Floor Washington, D.C. 20004

+1.202.974.2400 info@hudson.org www.hudson.org

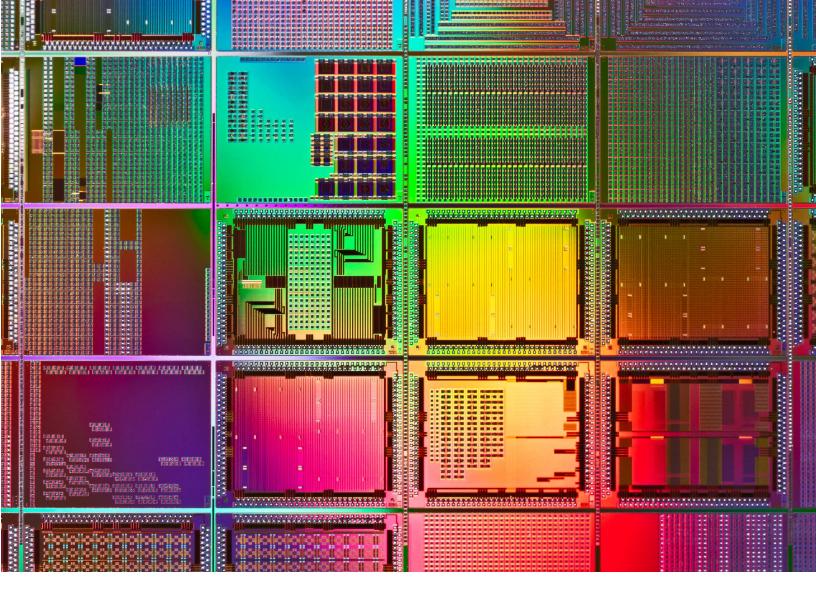

Cover: Light reflects through an integrated circuit. (Lawrence Manning/Getty Images)

Hudson Institute

JULY 2021

# Regaining the Digital Advantage: A Demand-Focused Strategy for US Microelectronics Competitiveness

BRYAN CLARK AND DAN PATT

CENTER FOR DEFENSE CONCEPTS AND TECHNOLOGY, HUDSON INSTITUTE

# ABOUT THE AUTHORS

# **Bryan Clark**

#### Senior Fellow and Director, Center for Defense Concepts and Technology

Before joining Hudson Institute, Bryan Clark was a senior fellow at the Center for Strategic and Budgetary Assessments (CSBA) where he led studies for the Department of Defense Office of Net Assessment, Office of the Secretary of Defense, and Defense Advanced Research Products Agency on new technologies and the future of warfare. Prior to joining CSBA in 2013, Mr. Clark was special assistant to the chief of naval operations and director of his Commander's Action Group, where he led development of Navy strategy and implemented new initiatives in electromagnetic spectrum operations, undersea warfare, expeditionary operations, and personnel and readiness management. Mr. Clark served in the Navy headquarters staff from 2004 to 2011, leading studies in the Assessment Division and participating in the 2006 and 2010 Quadrennial Defense Reviews. Prior to retiring from the Navy in 2008, Mr. Clark was an enlisted and officer submariner, serving in afloat and ashore submarine operational and training assignments, including tours as chief engineer and operations officer at the Navy's Nuclear Power Training Unit.

#### **Dan Patt**

## Adjunct Fellow, Center for Defense Concepts and Technology

Dan Patt focuses on the role of information and innovation in national security in his work at Hudson. Dr. Patt supports strategy at the artificial intelligence company STR and supports Thomas H. Lee Partners automation fund. He has more than fifteen years' experience operationalizing emerging technology including artificial intelligence, networked information systems, robotics, supply chain automation, and enterprise information technology. Dr. Patt also served as deputy director for the Defense Advanced Research Projects Agency's (DARPA) Strategic Technology Office (STO), managing more than \$400 million in annual technology investments in robust distributed systems architectures in a technology portfolio including battle management, command and control; communications and networking; intelligence, surveillance and reconnaissance; and electronic warfare. At DARPA he launched the Mosaic Warfare initiative. Dr. Patt received his B.A., M.S., and Ph.D. in aerospace engineering from the University of Michigan.

# The Center for Defense Concepts and Technology at Hudson Institute

Hudson Institute's Center for Defense Concepts and Technology examines the evolving field of military competition and the implications of emerging technologies for defense strategy, military operations, capability development, and acquisition. The center focuses on a comprehensive view: connecting strategy with new operational concepts; assessing the weapons and systems needed to implement new concepts; and evaluating the necessary commitment of resources.

# TABLE OF CONTENTS

| Chapter 1. Introduction                                                         | 7  |

|---------------------------------------------------------------------------------|----|

| Concentration—Not Globalization—Threatens the US Microelectronics Supply        | 8  |

| Chapter 2. Tiny Building Blocks of the Modern World                             | 10 |

| The Rise of Fabless Manufacturing                                               | 13 |

| Disaggregation and Threats to Supply Chain Reliability and Security             | 15 |

| Simplistic Solutions Based on a Simplistic Model                                | 16 |

| Chapter 3. A Framework for the Microelectronics Ecosystem                       | 17 |

| Four Key Factors with Which to Assess the Microelectronics Ecosystem            | 18 |

| Moving Up the Value Chain                                                       | 23 |

| Chapter 4. Applying the Framework                                               | 27 |

| Assessing the Microelectronics Ecosystem from the US Perspective                | 28 |

| Evaluating Potential Solutions                                                  | 30 |

| A Framework for Decision-Making                                                 | 36 |

| Chapter 5. A Strategy for Increasing Resilience, Assurance, and Competitiveness | 37 |

| Endnotes                                                                        | 40 |

# **CHAPTER 1. INTRODUCTION**

The microelectronics industry plays an outsized role in America's commercial and civic life. Although computers and electronic equipment only make up about 2 percent of US domestic output, they host financial and professional services that form half of the US economy and control nearly every durable consumer product and military system. Microprocessors are also a critical element of national infrastructure, as they manage all of America's energy grids, transportation systems, and telecommunications networks. Without a reliable supply of computer chips and microelectronic components, most US economic and societal activity would eventually grind to a halt.

The increasing reliance of products and services on microelectronics was brought into stark relief during 2021. Due to high capital costs and long lead times for new facilities, semiconductor supply chains were unable to quickly expand

output or change their product lines to meet rising orders as economies recovered from the COVID-19 pandemic. The resulting chip shortages slowed delivery of finished goods ranging from automobiles and refrigerators to video game consoles and medical devices; supplies are not expected to meet demand until 2022.<sup>2</sup>

To address the current chip shortfall, advocates renewed their longstanding calls for federal support to expand US semiconductor fabrication, which fell from nearly 40 percent in 1990 to just 12 percent of global production in 2020.<sup>3</sup> These

Photo caption: US President Joe Biden holds a microchip as he speaks before signing an executive order on securing critical supply chains in the State Dining Room of the White House in Washington, DC, February 24, 2021. (Saul Loeb/AFP via Getty Images)

proposals, however, are trying to solve the wrong problem. They could misallocate government funding to uncompetitive efforts while failing to invest in technologies that will improve US microelectronics resilience, assurance, and competitiveness for the long-term.

# Concentration—Not Globalization— Threatens the US Microelectronics Supply

Rather than representing flawed industrial policy, shrinking US semiconductor production merely reflects the microelectronics industry's disaggregation in response to market forces that incentivize manufacturers to outsource some production steps to specialists which can achieve lower cost and higher performance using their expertise and local government support. And even though most US-based microelectronics companies now fabricate their chips overseas, the United States remains the global semiconductor market leader, responsible for more than 45 percent of sales by value. US semiconductor companies' reliance on international suppliers resembles that of such US-based industrial champions as top-10 global carmakers Ford and General Motors, both of which average only 40% of domestically sourced content in their vehicles. 5

The disaggregation of US microelectronics production away from *integrated device manufacturers* (IDMs) like Intel is therefore a predictable evolution and does not necessarily represent a reduction in the resilience of US semiconductor supplies. On the contrary, today's US semiconductor shortages arguably result from microelectronics production being too concentrated. Although the chipmaking process is now spread across multiple companies and continents, each step in the supply chain is dominated by a few firms that have rationalized their capacity to meet current demand. As a result, localized disruptions have an outsized impact on overall output.

Fabrication is the most prominent example of semiconductor supply chain concentration. During the last 30 years, foundries located in Taiwan and South Korea displaced US, Japanese, and European IDMs to become market leaders in chip-making thanks to a combination of low regulatory costs, generous government grants, and tax breaks. Because fabrication plants cost billions of dollars to build and require frequent upgrades thereafter, countries having more highly diversified economies chose not to invest in national champion chipmakers. Consequently, more than 70 percent of global non-IDM semiconductor fabrication is now concentrated with Taiwan Semiconductor Manufacturing Company (TSMC) and South Korea's Samsung.

Supporters of subsidizing US chip fabrication argue overseas foundries create a risk that security vulnerabilities could be incorporated into microelectronics during fabrication.<sup>8</sup> Even though domestic foundries could increase ease of oversight, the most significant of recently reported semiconductor security flaws were introduced during chip design.<sup>9</sup> Instead, the more important security impact of the disaggregated microelectronics supply chain is that the resulting concentration leaves customers with few options to shift production when security concerns arise at a particular foundry.

Using government investment to bring more steps of the microelectronics production and assembly process onto US shores could help diversify the semiconductor supply chain and thereby improve resilience and assurance. However, without ongoing subsidies, US foundries may be unable to compete with TSMC or Samsung in affordably building the most sophisticated chips. Moreover, US partners and allies could be more effective hosts for new foundries if they have lower costs and a greater willingness to provide ongoing financial and regulatory support to national champion fabrication firms.<sup>10</sup>

Instead of reacting to temporary chip shortages or potential security vulnerabilities by reflexively onshoring the microelectronics supply chain's costliest elements, the focus of government interventions should be policy changes or investments that would provide the greatest leverage in improving US microelectronics competitiveness, resilience,

and assurance today and over the long-term. This study is intended to inform these decisions by providing a framework for assessing the microelectronics supply chain and evaluating government actions by objectively considering both sides of the microelectronics ecosystem—supply and demand.

This study's proposed framework suggests the US government has a historic opportunity to strengthen and secure the US microelectronics ecosystem by adopting a two-pronged policy and investment strategy using authorities granted by the 2021 National Defense Authorization Act (NDAA) and funding from proposed legislation designed to improve US competitiveness. <sup>11</sup> These Congressional actions are currently weighted toward production of today's IC technologies in which US fabrication and packaging are small players. Instead, they should prioritize research and development (R&D) of future architectures where the US microelectronics industry could gain an enduring advantage and market share.

The strategy's first line of effort would invest in the US microelectronics industry's future to provide it an advantage over foreign competitors by exploiting the emerging transition in chip design from simply increasing density to growing complexity and specialization in architecture and design. By focusing federal microelectronics investment on R&D of future IC technologies and manufacturing processes rather than production of today's chips, the US government could improve semiconductor supply resilience and assurance while restoring the US semiconductor producers to a competitive position across each segment of the supply chain.

To achieve these goals, however, government R&D investment cannot be limited to basic research but must also be used to bridge new microelectronics technologies through applied research to commercialization. Whereas the US government has

long invested in technology development, commercialization depends on an understanding of market demand, necessitating new mechanisms to guide government spending. Co-investing with US industry players through constructs such as public-private partnerships (PPP), built in the mold of SemaTech or In-Q-Tel, are a proven means of getting next generation technology to market. Government sponsors can provide an investment base that reduces risk to private investors while also shaping investment decisions to reflect government concerns and interests like security or operational utility.

To enable the strategy's main effort, its second prong calls for modest government funding to catalyze greater diversity in production of today's generation of chips, which would improve supply chain resilience and assurance and grow the fabrication and packaging capacity needed for future IC technologies. This line of effort would encourage market leaders TSMC or Samsung to build more US facilities in partnership with American firms and spur US companies like Global Foundries and Intel to expand domestic production by mitigating the higher cost of US operations through a combination of tax and regulatory incentives.

Government funding in the strategy's second prong would not be used for building and outfitting new plants but would instead focus on closing the operating cost differential between US and overseas production. As a result, the business case for new facilities would be improved, which could unlock private funding for facility construction and equipment. To further diversify microelectronics production, the strategy would employ purchase agreements, export controls, and technology sharing with US allies to encourage them to also host new fabrication and packaging capacity and help build a demand alliance that would counter China's desire to grow its industry's power in international markets.

# CHAPTER 2. TINY BUILDING BLOCKS OF THE MODERN WORLD

Integrated circuits (IC) are the most important elements in any microelectronic system, where they manage power supplies, store programs and data, sense the environment, and process data. At its most fundamental level, an integrated circuit (IC) is a collection of transistors created by joining two layers of material that is slightly conductive, such as a complementary metal-oxide semiconductor (CMOS). To enhance their ability to carry electrical current, one layer is doped with a metal having free electrons in its outer shell, and the other is doped with a metal having open positions in its outer electron shell. The right amount and type of doping ensures that the difference in energy levels between the free electrons and the holes is sufficiently narrow that application of a small voltage causes electrons to

jump from one layer to the other, thus generating a current and forming a transistor.

In an analog IC, the transistor's output current is varied continuously by varying the voltage applied to its layers, essentially making it an amplifier. Once the only form of IC, analog semiconductors are now used primarily in applications requiring variable output to reflect voltage input, such as photovoltaic cells, light-emitting diodes, and power-management systems.<sup>13</sup> Analog ICs can also support high-

Photo caption: An integrated circuit being manufactured on a silicon wafer. (Yellow Dog Productions/Getty Images)

voltage applications such as radars or amplifiers, in part by using semiconducting materials other than CMOS, such as gallium-arsenide and gallium-nitride (GaN).

In contrast to analog circuits, digital ICs use transistors as onoff switches. Digital ICs are mostly composed of silicon-based CMOS, because their relatively smaller band gap reduces power requirements and heat generation. For the current generation of digital IC designs, processing speed or storage capacity increases with circuit density. Today, features such as transistors in an IC are only 7 to 100 nanometers apart, requiring that chipmakers use lasers to etch circuits onto silicon wafers. By shrinking the laser's wavelength, millions of transistors can fit on a memory chip able to store gigabits of information or a microprocessor capable of performing billions of calculations per second. According to Moore's Law, circuit density and thus performance are expected to double approximately every 18 months, although the difficulty of etching ever smaller circuits and dissipating the heat they generate is beginning to constrain IC performance.14

A relatively small variety of architectures are used in memory chips. Static random-access memory (SRAM) chips can store large amounts of data and achieve the rapid transfer rates needed for applications like a video cache, whereas slower and less-expensive dynamic RAM (DRAM) chips are used to hold the data and programs currently in use by a microprocessor. Flash memory and electrically-erasable programmable readonly memory (EE PROM) ICs provide greater permanence compared to RAM for long-term storage. Give their narrow range of designs, memory IC manufacturers compete primarily on performance, and thus node size, resulting in the half-dozen companies able to build very dense ICs controlling more than 80 percent of the memory chip market.<sup>15</sup>

Unlike memory ICs, manufacturers produce microprocessors in a wide diversity of architectures from simple circuits for rote functions like timing or controlling vehicle emissions to the extremely sophisticated central processing units (CPUs) or graphics processing units (GPUs) used in computers and gaming consoles. Although capable of supporting a variety of functions, some CPUs and GPUs are specifically designed to efficiently run particular operating systems and work with specific computer hardware, such as the M1 chip used in Apple's new MacBook computers. A new generation of IC architectures is also emerging that combine elements of CPUs, GPUs, and memory to support the unique information flows required for effective artificial intelligence (Al)-enabled operations. <sup>17</sup>

Although highly versatile, CPUs and GPUs are not the best microprocessors for all situations. *Application-specific integrated circuits* (ASICs) are built to provide a narrow set of characteristics that yield optimal performance in particular use cases, often hosting tailor-made software. Although their specialization generally makes ASICs more expensive than CPUs or GPUs, they can be more affordable when purchased in large quantities. In contrast to general CPUs, ASICs can provide critical performance advantages by only incorporating those design elements needed for them to perform their intended function. ASICs are often used in digital signal processors or the control systems of medical devices, home appliances, and automobiles, where power efficiency, low latency, and reliability are priorities.<sup>18</sup>

The other main type of specialized microprocessor is the *field* programmable gate array (FPGA). Whereas an ASIC is designed with a particular architecture, FPGAs allow the component manufacturer to configure the circuit's transistor arrays using software. Because their physical design is not specialized, tailoring FPGAs to fit specific applications is less expensive than creating ASICs to do so, but FPGAs must be reprogrammed to support each new use.<sup>19</sup>

Efforts to improve CMOS IC speed or capacity by reducing feature size are approaching physical and manufacturing limits. To continue increasing performance, chipmakers are beginning to pursue more disaggregated chip designs, such as *systems*

Figure 1: Comparison of microprocessor (digital logic chip) types

| TYPES OF MICROPROCESSORS |        |        |        |           |

|--------------------------|--------|--------|--------|-----------|

|                          | CPU    | GPU    | FPGA   | ASIC      |

| Compute adaptability     | High   | Medium | Low    | None      |

| Compute power            | Medium | High   | High   | Medium    |

| Latency                  | Medium | High   | Low    | Ultra-low |

| Throughput               | Low    | High   | High   | High      |

| Parallelism              | Low    | High   | High   | High      |

| Power efficiency         | Medium | Low    | Medium | High      |

Source: Authors; based on Arnon Shimoni, "A gentle introduction to hardware accelerated data processing," Hackernoon.com, August 27, 2018, https://hackernoon.com/a-gentle-introduction-to-hardware-accelerated-data-processing-81ac79c2105.

on a chip (SoC) that combine multiple ICs into a single package and systems in a package (SiP) that integrate CMOS and non-CMOS ICs.<sup>20</sup> In many existing microelectronics designs, memory chips and microprocessors are separate and mounted on circuit boards to enable different system configurations and allow various suppliers to provide ICs for a system. However, this architectural approach introduces latency due to the distance between components. In an SoC, all the ICs for an application are combined within a single chip, reducing the distances between them and enabling a wider variety of architectures. Although SoCs can be built from a set of complete ICs, the SoC approach allows the use of partial ICs or "chiplets" that may not include all the features of a stand-alone chip and which are attached to a common substrate or physically stacked onto one another to form complete 2.5D or 3D circuits.<sup>21</sup> The customization possible with an SoC is similar in intent to an ASIC, but an SoC can mix commodity and specialized chip types, thus opening up a design space for lower-cost solutions compared to an ASIC.<sup>22</sup>

Although IC performance is improving much faster than that of other products, the microelectronics industry is also very mature. Like other mature manufacturing sectors, older IC

designs and architectures are still in wide use and continue to be produced by more companies than are building the most sophisticated chips with the smallest node sizes. For example, the chips shortages being experienced in the aftermath of the COVID-19 pandemic are most acute among the legacy, large-node semiconductors that have replaced many of the analog electrical control systems in appliances and vehicles.

The production process for old and new semiconductors evolved in response to market forces. Semiconductor manufacturers and service providers thrived in locations with local expertise and low costs for labor, regulatory compliance, and utilities, as well as robust government financial support in the form of subsidies or tax reduction. Improved shipping efficiency and management encouraged specialization by lowering the cost to move products between steps of an industrial process.<sup>23</sup> As a result, before most chips are installed in mobile phones or other consumer electronics, they and their constituent raw materials will have passed through a dozen or more companies located on two to three continents. Thanks to real-time data analysis and dependable shipping, global microelectronics production is now optimized to deliver components just in time for the chain's next step.<sup>24</sup>

# The Rise of Fabless Manufacturing

Microelectronics manufacture was not always globalized. During the rise of personal computing in the late 20th century, America's Intel was the predominant supplier of PC microprocessors, building CPUs for market leader IBM as well as upstart competitors Dell, Compaq, and Hewlett-Packard. Although it relied on overseas companies for raw materials and some manufacturing equipment, as an IDM Intel created the chip architecture and design in addition to conducting every step of the production and sales process.<sup>25</sup>

Intel's dominance in the consumer CPU market began to erode with the rise of mobile devices and the emergence of new manufacturers that specialized in parts of the IC production process, particularly those where they could integrate

horizontally to achieve efficiencies and lower costs than an IDM.<sup>26</sup> The advent of specialized chip foundries like AT&T, LSI Logic and VLSI Technology made possible *fabless chip manufacturing*, in which a company designs its own chips that a foundry builds under contract. The availability of electronic design automation (EDA) tools built by software makers like US-based Cadence and Synopsis further spurred expansion of the fabless model.

Fabless manufacturing has been used for decades by American chipmakers including Broadcom, Nvidia and Qualcomm.<sup>27</sup> Apple joined the ranks of fabless manufacturers in 2017 with its A11 mobile phone microprocessor, expanding to laptops and tablets in 2020 with the M1 CPU.<sup>28</sup> And in a major capitulation to the fabless trend. Intel announced in 2021 it would use overseas

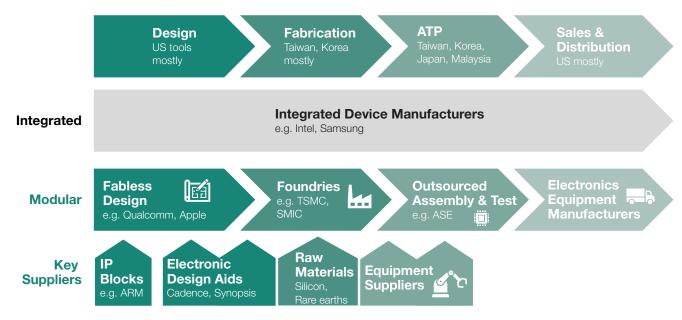

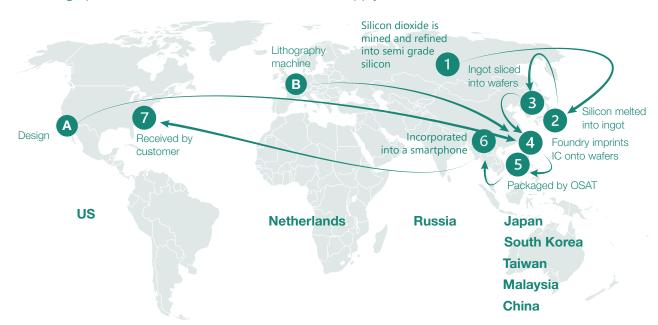

Figure 2: The semiconductor supply chain

Microelectronics manufacturers produce semiconductors and assemble them into finished circuits and modules for customers to incorporate into their systems.

Source: Authors

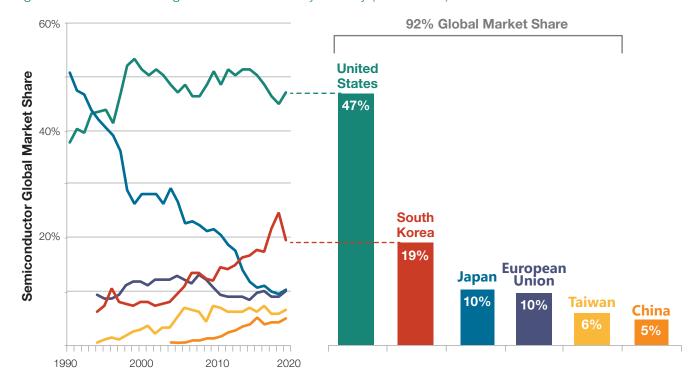

Figure 3: Semiconductor global market share by country (1990-2020)

US companies dominate the global market share in semiconductors, even as lower value-added functions of fabrication, packaging, and assembly have shifted overseas. China has only captured 5% of the global market despite tremendous investment.

Source: "2020 State of the US Semiconductor Industry," Semiconductor Industry Association, June 2020, https://www.semiconductors.org/wp-content/uploads/2020/06/2020-SIA-State-of-the-Industry-Report.pdf.

foundries to build some of its chips after failing to achieve stateof-the-art node sizes in its own fabrication facilities.<sup>29</sup>

Free to focus only on building ICs that other companies design, foundries compete primarily on price and node size. Each move toward smaller features costs more to create, build, and execute, but yields higher performance increases per unit cost compared to the previous generation. Through technology investments and close relationships with the leading US fabless manufacturers Samsung and TSMC steadily gained market share and eventually dominated semiconductor fabrication. Today, TSMC and

Samsung make 70 percent of contracted chips overall and all the highest-performing chips that have node sizes of less than 7 nm.<sup>30</sup>

Specialization has also extended to other steps of the IC production process. Samsung and TSMC depend on Dutch firm ASML for the extreme ultraviolet (EUV) light etching machines needed to create the small features in high-end chips.<sup>31</sup> To reduce costs and overhead, foundries also outsource the assembly, test, and packaging (ATP) process of cutting etched silicon wafers into chips and preparing them to be installed in a customer's systems.

Despite semiconductor manufacturing's disaggregation, US companies still lead the global chip market due to their strengths in design and sales. As shown in Figure 3, US semiconductor market share remained above 40 percent and rose during the past 30 years, largely at the expense of Japanese chipmakers. The United States has sustained its lead in semiconductor sales by embracing rather than resisting globalization because, while Intel remains an IDM, most other US chip suppliers employ a fabless model for all or some of their products.

In addition to prompting concentration, specialization in semiconductor production initiated a race to the bottom among service providers and fabricators with respect to price that—along

with government subsidies in some cases—has reduced profit margins and now dissuades competitors from entering the market. This barrier to entry is most challenging for chip fabrication plants, which cost about \$4 billion to construct and equip for the manufacture of ASICs like those used in vehicles and medical devices and more than \$15 billion to produce the latest GPUs or CPUs.<sup>32</sup>

# Disaggregation and Threats to Supply Chain Reliability and Security

The semiconductor industry, like other commodity-based industries driven by a relentless push for efficiency, periodically suffers supply chain disruption when production capacity is lost or customer demands change. The COVID-19 pandemic

Figure 4: Geographical distribution of the semiconductor supply chain

Today, the semiconductor supply chain is widely distributed, with a product passing through many different geographic locations before reaching its final destination. The geographic concentration of many elements in Asia constitutes a geopolitical concern. Establishment of US foundries cannot, by itself, solve global resilience issues, and alliance-based approaches are required to increase resilience in the semiconductor supply chain.

Source: Authors

combined with the considerable increase of semiconductor content in most every durable product caused a greater than normal supply chain disruption during 2021.<sup>33</sup> And although today's shortages resulted in part from a global health crisis, the next disruption could be geopolitical. As shown in Figure 4, most steps in semiconductor manufacturing are concentrated in East Asia, where they could be subjected to pressure or coercion by the government of the People's Republic of China (PRC) or become geographically isolated from US designers and customers were shipping networks to break down.

Disaggregation of microelectronics supply chains also raises concerns among manufacturers and customers that their chips have been constructed as intended and as advertised and are free of security vulnerabilities. Although fabless semiconductor companies design their own ICs, outsourcing fabrication, packaging, and testing in the United States or overseas could increase opportunities for the introduction of inadvertent bugs, flaws, or intentional back doors, which hackers could use to access or turn off a circuit. Such security vulnerabilities are of greatest concern in chips destined for national security applications such as controls for critical infrastructure or weapons systems purchased by the US Department of Defense (DoD).

To assure their microelectronics are free of bugs and back doors, fabless companies employ extensive quality control measures during and after manufacture.<sup>36</sup> However, threats to semiconductor security will likely grow as chip lifecycles lengthen, increasing the time hackers have to find and exploit potential vulnerabilities and develop attacks. Potentially the most important impact of supply chain disaggregation on assurance is that even if testing and oversight are effective, concentration of microelectronics production with a few manufacturers reduces customer options in choosing an IC supplier and may preclude switching suppliers to address a security concern. Partly to improve assurance, the US government authorized in 2020, but has not yet appropriated, funding to support construction of more semiconductor fabrication facilities in the United States.<sup>37</sup>

# Simplistic Solutions Based on a Simplistic Model

Although questions about microelectronics availability and security are legitimate, the answers proposed by the US government and industry to date are based on a simplistic supply chain model that fails to account for demand and the increasing technological complexity of microelectronics. Rather than developing in isolation, today's microelectronics supply chain configuration is a response to dynamic market forces exerted by current and prospective customers. The microelectronics supply chain could therefore be more properly characterized as the *microelectronics ecosystem*.

As evidenced by recent government action and calls from the semiconductor industry, the most prominent initiative being pursued to improve resilience of and customer assurance in microelectronics production is public subsidies for US chip fabrication. However, this one-size-fits-all solution does not necessarily secure US microelectronics manufacture, which can accrue security vulnerabilities throughout the production cycle, whether located in the United States itself or elsewhere. Onshoring fabrication also fails to account for current and future demand, which could render new US-based fabrication facilities uncompetitive or technologically obsolete and therefore unable to ensure chip supplies. A more comprehensive approach is needed to better assess the microelectronics ecosystem in order to develop approaches to increase its resilience and its assurance for US customers.

The framework proposed within this study, which is based on a more thorough evaluation of the microelectronics ecosystem, incorporates its wide variety of elements and relationships, the influence of today's semiconductor market, and the importance of adding value to support future demand. In addition to enabling improved risk assessments of the current supply chain, the proposed framework enables a more realistic evaluation of potential government policies or investments in preventing future chip vulnerabilities or shortages, while positioning US chipmakers to become more competitive in the global microelectronics market.

# CHAPTER 3. A FRAMEWORK FOR THE MICROELECTRONICS ECOSYSTEM

Most models of the microelectronics supply ecosystem include only the supply-side contributions of product and service providers. <sup>39</sup> In relatively stable industries such as automobile or appliance manufacturing, supply chain assessments may be sufficient to inform effective government policies. In comparison to these industries, however, the microelectronics market is more dynamic, with fresh IC designs and software architectures emerging nearly continuously in response to new use cases, security liabilities, or the need to provide additional value for prospective customers.

In the microelectronics ecosystem, supply-side solutions are likely to eliminate only temporarily an IC shortage, close off one

class of security vulnerability, or prop up a US semiconductor supplier for the near-term. To provide more enduring solutions, the US government should consider current and future demand to assess whether government interventions are likely to be sustainable and produce their desired effects.<sup>40</sup>

To guide government policies and investments that promote security, semiconductor availability, and increased US competitiveness, this study proposes a framework comprising four factors, measured from the perspective of the US microelectronics

Photo caption: An engineer uses a digital tablet for quality inspection in an automated production line. (Nitat Termmee/Getty Images)

Figure 5: Factors addressed in the proposed microelectronics ecosystem assessment framework

| RESILIENCE                                                                                                                                      | ASSURANCE                                                                                         | DEMAND                                                                                                                                                       | NEW VALUE                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Definition: Can US customers (consumers and DOD) reliably receive materials and equipment?                                                      | Definition: Can vulnerabilities and exploits be introduced that would not be detected in testing? | Definition: Is there a market for US players in current and near-term tech, as driven by (largely commercial) global demand.                                 | Definition: How can US companies be leaders in next-generation technologies?                                                          |

| Opportunity: Achieving a microelectronics supply that is resilient to Chinese influence, war, natural disaster, or capricious government policy | Opportunity: Confidence that microelectronics components are free from exploits and vulnerability | Opportunity: Meeting and harnessing near- term global market demand for microelectronics, and the healthy businesses and economic activity that accompany it | Opportunity: Producing new and emerging technologies that will address future market demand, creating new virtuous cycles of industry |

Source: Authors

customers and industry: resilience of continued microelectronics supplies to the US market; assurance that US microelectronics reflect their intended design and are free of security vulnerabilities; the ability of the US microelectronics industry to meet current microelectronics demand, which shapes the ecosystem; and the value added from US firms, which supports future demand. Assessing each element of the current microelectronics supply chain through these four lenses can highlight priority areas for US government intervention as well as evaluate the potential impact and sustainability of proposed policies or investments.

# Four Key Factors with Which to Assess the Microelectronics Ecosystem

# Resilience

Microprocessor shortages for applications ranging from gaming consoles to automobiles and medical devices highlight the

challenges to resilience posed by microelectronics production specialization and concentration. Today, TSMC and Samsung build all high-density microprocessors having less than 7 nm features, which power the most highly sophisticated computing devices. Intel is working to regain parity, while a larger number of companies build the less-advanced semiconductors with larger node sizes used in other consumer electronics, military systems, and critical infrastructure. Because their profits are lower compared to high-end semiconductors, fabrication capacity of larger node size chips such as those used in automobiles has evolved to meet demand and switching the type of IC a given facility produces can take months to complete. Consequently, a combination of facility fires in Japan and ice storms in Texas recently disrupted vehicle IC supplies for almost a year.

Besides foundries, a small number of providers have a dominant share of the market in other major steps in the microelectronicsproduction process such as manufacturing equipment or ATP. Of the steps comprising the semiconductor production process, only design and IC integration into equipment have significant supplier diversity.

Geopolitical disruptions also pose a threat to microelectronics resilience. The concentration of chip fabrication, packaging, and testing performed in Taiwan creates a risk of severe disruption or complete interdiction of supplies should that country's government come under pressure from the neighboring PRC regime, which depends on Taiwan for semiconductors. Although a PRC invasion of Taiwan is unlikely and mainland China is Taiwan's largest trading partner overall, the PRC government regularly interferes with Taiwan's computer networks and electromagnetic spectrum. It also possesses the air and naval capabilities to block Taiwan's access to raw material imports and semiconductor customers should it decide to do so.45 The threat of military action coupled with economic coercion and information warfare could prove sufficient to convince Taiwan to limit its companies' participation in the global microelectronics ecosystem, although the economic consequences for Taiwan could be severe.

National security applications, which comprise about 10 percent of overall US semiconductor demand, arguably constitute the area of greatest concern with respect to microelectronics ecosystem resilience. The DoD initiated a trusted foundry program in 2003 to ensure secure production of chips for use in defense systems, but trusted foundries currently provide only about 2 percent of DoD ICs.<sup>46</sup> US national security applications therefore remain dependent on the relatively concentrated IC production base, especially in Taiwan.

To be effective, policies intended to increase microelectronics resilience should consider concentration in each step of the production process and across all IC categories. For example, blanket proposals to fund foundries in general ignore the fact that some chip types have much more greatly concentrated fabrication segments than others. And beyond fabrication, US

government investment could achieve greater impact per cost by establishing domestic ATP providers, which are currently concentrated in Taiwan, Japan, Korea, and Malaysia.

## Assurance

Security vulnerabilities can be introduced at all stages of the microelectronics supply chain, as shown in Figure 6, but *verification testing*, which verifies that an IC has been built according to its design, and *validation testing*, which determines whether or not a circuit performs as it was intended to, can reveal many such liabilities. In the context of this study, *assurance* is defined as the ability to detect security vulnerabilities through hardware *verification and validation* (V&V) *testing*<sup>47</sup> or by other advanced design and architectural features that stymie malicious actors.

Microelectronics vulnerabilities can be classified into three primary categories: flaws, bugs, and back doors. Component manufacturers and service providers can unintentionally incorporate *bugs*, which are due to inconsistency between chip design and as-built configuration, or *flaws*, in which faulty design causes an IC to either fail or be unable to perform its intended function. In contrast, *back doors* are deliberately and illicitly incorporated into hardware by semiconductor suppliers, packagers, software companies, or other bad actors and can then later be activated to disable, slow, disrupt, or clear the system's memory at a predefined moment in time or can activate a hidden circuit in response to an external signal. Back doors can also be used to introduce hidden features into a system, such as circuits that exfiltrate data using an electromagnetic emission or stray signal that the exploiting party is prepared to receive. <sup>48</sup>

Although bugs, flaws, and back doors pose significant security challenges no matter where they emerge, their presence is most consequential in national security microelectronics applications such as DOD weapons systems and critical power, communications, and transportation infrastructure. 49 US peer competitors such as the PRC and Russia would in all likelihood invest substantial effort and funding into developing

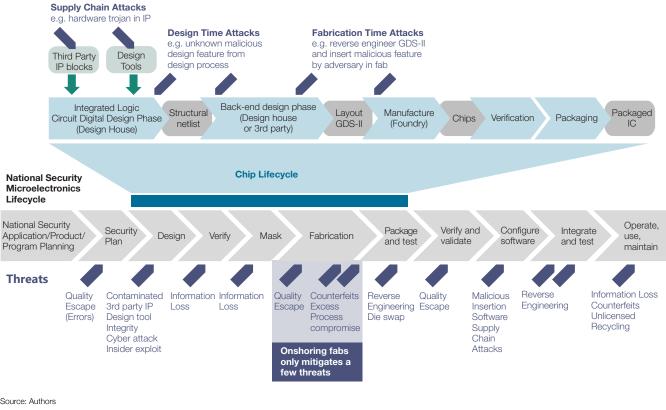

Figure 6: Security vulnerabilities in the microelectronics lifecycle

Source: Authors

back doors capable of avoiding detection through V&V. DoD's trusted foundry program was intended to address the threat of intentionally introduced microelectronics vulnerabilities, but only supplies a small percentage of DoD's total IC demand. Moreover, the complexity of modern microelectronics is such that even an IC that has been domestically fabricated, validated to have no known vulnerabilities, and verified as having been properly manufactured, unanticipated security flaws can still be discovered subsequent to the system being fielded. This occurred in 2021 when attack opportunities in the Micro-Op Cache of some Intel ICs was discovered.50

Opportunities to insert intentional vulnerabilities will likely increase as computer programs known as firmware play an increasingly important role in hardware operation. FPGAs already use firmware to program their gate or transistor configuration, and SoC designs require firmware to manage information flows between different chiplets or layers of complex ICs. Although programmed into a chip and not intended to be easily changed following production, firmware instructions could be written so as to provide still another access point through which to interfere with an IC's operation or exfiltrate data.<sup>51</sup> Conversely, firmware also presents an opportunity to mitigate upstream vulnerabilities by modifying system behavior in ways unanticipated by a malicious actor.

Rather than increasing assurance solely through creation of trusted ICs, more promising approaches to future microelectronics security are technological in nature. In these approaches, users would view individual ICs as *untrusted*, but could view as *trusted* the overall circuit or SoC in which individual ICs are integrated.<sup>52</sup> DoD is currently pursuing a zero-trust model for microelectronics assurance in which improved design features and testing approaches prevent or detect vulnerabilities or–should they be present but not be detected or eliminated–minimize the harm they can cause. Included in these efforts are disaggregated SoC designs using heterogeneous components, including chiplets, in which the final circuit configuration is unknown to fabrication and ATP providers, thereby reducing the ability of adversaries to introduce effective back doors.<sup>53</sup>

As noted in Chapter 1, onshoring fabrication facilities within the United States will not by itself achieve microelectronics assurance. Vulnerabilities could be introduced in design or production steps other than fabrication, and US foundries would not be immune to the introduction of bugs, flaws, or back doors into ICs. However, greater diversity of fabrication and ATP facilities would, at some cost in time and money, offer customers alternative suppliers when security concerns arise at an existing provider. Over the long term, developing and adopting new approaches to obtain trusted microelectronics from untrusted sources will constitute a more effective and robust approach to achieving security compared to increasing domestic IC production.

#### Demand

The microelectronics ecosystem's configuration has always reflected the needs of contemporary use cases. For example, customers' pursuit of lower prices and improved performance

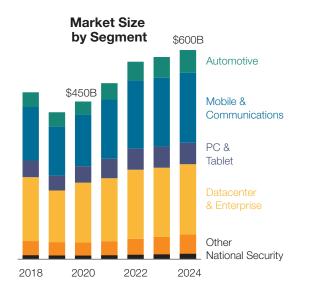

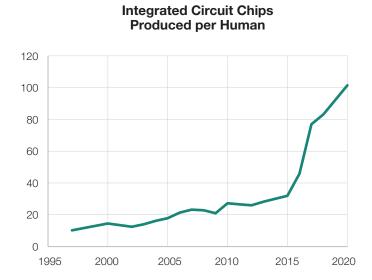

Figure 7: Microelectronics market growth

The overall microelectronics market is growing, led by increases in automotive, data center, and enterprise demand.

Figure Source: Authors, Data Source: Semiconductor Industry Association and original research by the authors.

incentivized supply chain disaggregation and the concentration of most supply chain steps among a small number of performers. Across all IC applications, vehicle controllers, data center microprocessors and memory, and telecommunications modems and processors are experiencing the highest growth rates. <sup>54</sup> The ecosystem has therefore evolved to include around a dozen makers of chips like those used in automobiles and data centers; growth in high-end computer microprocessors is constrained by the challenges associated with small-node semiconductor manufacturing. <sup>55</sup>

As shown in Figure 7, the microelectronics industry currently produces more than 100 chips per year per human, and the industry's products include an expanding range of designs and sophistication—triple the output of five years ago and with no signs of slowing. Given the dynamism of IC demand and the reactive nature of manufacturing, expecting supply-side policies to effectively shape microelectronics ecosystem structure is naïve.

Demand should therefore be a significant consideration in the development of policy and funding proposals designed to improve the US microelectronics ecosystem. Government initiatives that do not support customer expectations with respect to price, performance characteristics, and availability are unlikely to penetrate the ecosystem and achieve their intended goals of increased resilience, assurance, or competitiveness. Moreover, policy and investment interventions that fail to satisfy current demand will be unsustainable without continuing government support.

#### Value Added

In addition to current demand, the microelectronics supply chain is shaped by the profit associated with differing IC types and the value added by various production steps. For example, although relatively small-node CPUs and GPUs boast higher profit margins than do other ICs, the fabrication plants that build small-node types require the greatest upfront capital investment and require frequent equipment and

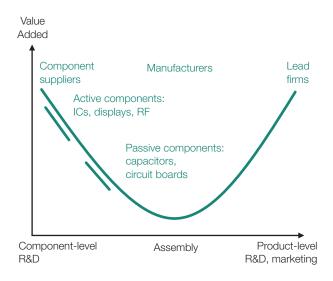

Figure 8: The "smiling curve" of value-added in electronics production

Source: Namchul Shin, Kenneth L. Kraemer, and Jason Dedrick, "Value Capture in the Global Electronics Industry: Empirical Evidence for the "Smiling Curve" Concept," Industry and Innovation, Vol. 19, No. 2, 89–107, February 2012. http://dx.doi.org/10.1080/13662716.201 2.650883

facility upgrades to keep pace with the latest advances. In contrast, less sophisticated, large-node ICs garner lower profits but entail relatively smaller up-front costs and are often made at existing fabrication plants that no longer build leading-edge semiconductors. These contrasts in size of initial outlay and upgrade requirements, coupled with ample demand, incentivize a large number of manufacturers to produce older-design memory, control, and timing ICs whereas only the two incumbents currently build high-performance, small-node ICs with node sizes of less than 7 nm.

The number and diversity of microelectronics equipment and service providers are also influenced by the contribution of their efforts to the overall price or performance of final products, with those delivering the most impact contributing the highest value added. Consequently, the microelectronics supply chain can also be characterized as a *value chain*. Production steps

Figure 9: US market share of the semiconductor value chain

US firms are focused on the higher value areas of the microelectronics ecosystem.

Figure Source: Authors, Data Source: BCG Analysis, Original Research, SIA Data

that add greater value are often more profitable, but also offer greater challenges to effectively implement because of the relatively higher investment or greater technical proficiency they require. <sup>56</sup> As argued by Namchul Shin and demonstrated by subsequent research (see Figure 8), the greatest value-add occurs on the two ends of the production process: on one end, component-level research and development (R&D) and manufacture of sophisticated components needed for the product, e.g., small-node microprocessors, and, on the other end, R&D, marketing, and branding of the overall product, such as an iPhone. Assembling components into products and producing such commodity ICs as controllers or timing chips fall in the middle and offer the lowest value added. <sup>57</sup>

Structural currency disadvantages and high labor prices in the United States incentivize US manufacturers to focus on those

portions of the production process which have the highest value added and can therefore command premium prices (see Figure 9). In contrast, the focus of relatively new entrants into the industry based in Taiwan, the PRC, and South Korea is still predominantly component production and assembly, which, although essential, offer lower value and profits. Asian firms currently attempting to move up the value chain to new disaggregated or SoC and SiP architectures are hindered by the need to obtain scarce design talent and US-built EDA tools and manufacturing equipment, as well as the "innovator's dilemma," or the need to devote resources and capability to shrinking nodes sizes in their current designs instead of retooling to introduce next-generation technologies.<sup>58</sup>

In addition to shaping the current microelectronics ecosystem, the value added by different production segments reflects their ability to address future demands. High value-added products and services—e.g., improved design tools, new classes of manufacturing equipment, and innovative core IP capable of increasing diversity in computing architectures—will be central to developing and fielding new ICs that provide increased levels of performance and security through small node size, disaggregated designs, and increased heterogeneity. The rising importance of complex architectures will also increase the value added associated with ATP, making it a potentially attractive area for US government investment. <sup>59</sup>

# Moving Up the Value Chain

The microelectronics ecosystem encompasses production elements characterized by their relative degrees of resilience and assurance; customers wanting microelectronics to use in current applications; and prospective customers seeking ICs with improved performance and security for existing or new use cases. As shaped by a relatively free market, today's ecosystem effectively aligns supply with demand and responds to evolving customer expectations or exogenous shocks such as the COVID-19 pandemic. The fact the ecosystem works, however, does not mean it is problem-free, as evidenced

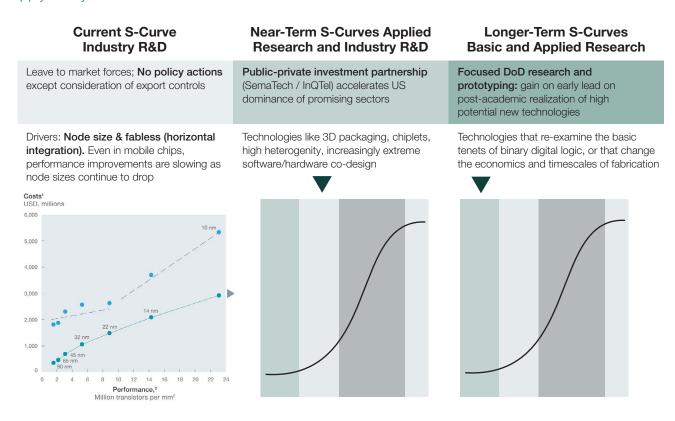

Figure 10: S-curve growth models reflecting different technologies in the microelectronics supply ecosystem

The microelectronics supply ecosystem encompasses current, near-term, and long-term technologies that develop along "S-curves" characterizing their development.

Source: Authors

by the existing and potential resilience and assurance shortfalls described in Chapter 2. Government intervention may be needed to address these concerns and help the US microelectronics industry remain competitive as rivals in China, Taiwan, and South Korea move up the value chain into design, component R&D, and product development.

In pursuing resilience, assurance, and competitiveness, government efforts should be sustainable and target areas

that offer the most leverage. For example, although the US government could fund construction of additional US fabrication and ATP capacity for current-generation chips, overseas competitors such as national champions TSMC and Samsung would still retain advantages based on their proficiency, existing customer base, lower labor costs, and pervasive government financial and regulatory support. Consequently, prices for US-built ICs would most likely be higher than comparable ones built abroad, and ongoing federal support would be needed to keep

US fabrication facilities in business. <sup>60</sup> US government funding could be used more effectively to close the cost differential between US and overseas fabrication or ATP, which would make the business case for US production facilities more attractive and enable US firms to obtain corporate or other private funding for expansion or new construction.

Supporting ongoing fabrication or ATP operations would require less funding compared to construction or equipment and could enable more US government investment toward R&D of new semiconductor technologies in which US chip companies can establish an advantage, similar to the initial development of ICs during the mid-20th Century. Government resources will be essential to future microelectronics competitiveness, considering the multi-billion-dollar annual R&D investments being made by foreign competitors such as TSMC.<sup>61</sup>

Typically, the US government funds basic research into potentially useful new technologies and provides episodic, project-based funding for applied research into promising advances that emerge from basic research. The US microelectronics industry also invests in R&D, but its aim is usually evolutionary improvements on existing commercial technologies that are already fielded. As shown in Figure 10, today's mature IC technologies, which achieve incremental performance improvements or security gains over time, occupy the upper flat portion of their developmental "S-curves." These sustaining technologies typically follow Moore's law and increase performance through industry-sponsored R&D, which enables them to increase scaling and achieve greater transistor density.

However, little of either US government or corporate investment is typically directed at closing the gap between applied research and commercially viable products. This is a problem experienced particularly by DoD and is characterized as the "valley of death" for new defense technologies. Within the microelectronics ecosystem, this gap occurs because government sponsors are unfamiliar with semiconductor market dynamics and do not

know what technologies could be commercially viable or how to best market them; manufacturers are frequently unable to justify to their shareholders long-term investments in unproven technologies; and venture capital firms are reticent to invest in the microelectronics industry because of its high capital intensity and distant returns on investment.

Future technologies offer more leverage for government investment than do current technologies because they exploit the United States' position as a leader in high value-added component and product design, production of manufacturing equipment, and marketing and distribution. With respect to near-term future IC technologies occupying the steep portions of their S-curves and just entering the market, US microelectronics firms could, through government-sponsored applied research, expand beyond their existing strengths at the ends of the smiling curve of Chapter 3 and diversify into ATP, which will be critical to new disaggregated architectures such as SoC, SiP, and 2.5 or 3D chips. These efforts would build on government incentives provided to increase fabrication in the United States. Near-term future technologies also offer relatively certain and proximate returns on investment, making them more attractive to private capital. A public-private partnership (PPP), like those employed by In-Q-Tel and SemaTech, could fill the gap for these technologies between applied research and commercialization. Government co-investment in the partnership would catalyze the deployment of private capital while also benefiting from insights of private investors regarding market and demand trends.62

Future technologies just beginning to move up the S-curve are unlikely to attract private capital to the same degree as more mature near-term advances, because their returns are rightly viewed as less certain and more distant. Long-term microelectronic technologies are generally pursuing performance characteristics that exceed those governed by Moore's law for CMOS-based semiconductors and include such approaches as *mixed-signal* chips which combine analog and digital ICs,

complex 3D SoCs, and non-CMOS semiconductors and architectures designed for high-power applications or quantum computing. Government-sponsored basic and applied research will therefore be required to develop long-term IC technologies.<sup>63</sup>

When they have matured and moved farther up their S-curves, long-term technologies could transition into commercial use via a PPP, such as in the evolution of GaN semiconductors from military radars to 5G radios. <sup>64</sup> Other new technologies could have primarily military or government applications and only modest commercial ones and may depend on continued government funding.

The proposed framework of resilience, assurance, demand, and value added provides a more holistic way to assess the microelectronics ecosystem than simply identifying chokepoints and bottlenecks in today's supply chain. Since the objective of employing a supply chain model is to guide actions intended to improve the chain's functioning, incorporating future as well as current customers is essential to estimate the likelihood of potential initiatives being effective and enduring. In the next chapter, the proposed framework will be applied to existing and potential future proposals currently under consideration for US government intervention into the microelectronics ecosystem.

# CHAPTER 4. APPLYING THE FRAMEWORK

The microelectronics industry has long argued that the US government should grow domestic fabrication capacity in order to counter the East Asian concentration of foundries and improve IC resilience and assurance for national security applications. <sup>65</sup> Although fabrication is the most visible and capital-intensive part of microelectronics production, it is not the only chokepoint with the potential to affect IC supply resilience, and US government funding may achieve a greater impact by advancing the introduction of new chip technologies where the US microelectronics industry can establish an advantage. The 2021 NDAA's CHIPs Act and DARPA's Electronics Resurgence Initiative recognize the need for a more holistic approach to government intervention by including options to develop new technologies alongside funding new fabrication and ATP facilities. <sup>66</sup>

The four-factor framework proposed in this study enables a systematic way to identify production segments for which federal policy or funding might be warranted and beneficial. Because the framework is intended to guide US government interventions, the potential impact of each segment on IC resilience, assurance, demand, and value added is evaluated from a US perspective. To represent US customers, resilience and assurance are measured in terms of ICs supplied to the US market from the global supply chain; to represent US manufacturers, demand reflects the ability of US companies to address contemporary market needs; and value added assesses the US microelectronics industry's ability to add value via that production segment.

Photo caption: A scientist examines an electronic display depicting a silicon wafer. (Monty Rakusen/Getty Images)

Figure 11 summarizes application of the four-factor framework to the current microelectronics ecosystem based on recent assessments by a range of industry, academic, government, and trade organizations, including the Semiconductor Industry Association, International Electrical and Electronics Engineers (IEEE), Congressional Research Service, and National Cyberspace Solarium Commission. <sup>67</sup> This assessment is subjective, of course, and other analysts may interpret the state of the microelectronics ecosystem differently. This study's main argument is that a comprehensive framework such as the one depicted in Figure 11 is needed to provide a starting point for formulating government policy and investment in the IC area. Each segment's assessment is briefly described below.

# Assessing the Microelectronics Ecosystem from the US Perspective

#### Fabrication

The concentration of fabrication capacity into a relatively small number of facilities reduces the fabrication segment's resilience, and exacerbating this reduction is the geographic clustering of capacity for some IC types, such as <7 nm node size GPUs and CPUs, which are only produced in Taiwan and South Korea. Because testing can often detect backdoors, this level of concentration need not reduce assurance, but the lack of fabrication diversity reduces options when a customer is dissatisfied with a foundry's efforts to eliminate such vulnerabilities. Sometimes testing can detect flaws and bugs, but V&V is often only able to catch known phenomena and is an incomplete solution for assurance.

The focus of US fabrication facilities, which supply about 12 percent of today's demand, is legacy chip types that can be profitable despite the US's relatively high-cost structure. US fabrication firms could gain an advantage if they were to lead in the introduction of new technologies such as SoC or 3D and heterogeneous ICs that incumbent fabs overseas may be less well-positioned to adopt due to their need to support

current customers with sustaining advancements along today's S-curve. However, new chip architectures depend on leading-edge fabrication capabilities that are only present at small scales in the United States, which will require some improvement in high-end US-based fabrication capacity.

## Packaging

The ATP segment of semiconductor production separates etched silicon wafers into chips and prepares them for installation in customer systems by incorporating connectors and mounting hardware or in some cases combining ICs into higher assemblies such as SoCs or SiPs. Although generally not as concentrated as fabrication, packaging for the most sophisticated chips is becoming increasingly limited to a few firms with the requisite equipment and skill. The geographic clustering of ATP firms in East Asia reduces resilience but impacts assurance less severely since packaging offers few opportunities for exploitation.

Expanding packaging to the United States would be challenging due to relatively higher labor and regulatory costs. However, US microelectronics manufacturers moving up the value chain to SoC, 3D, and heterogeneous chips could also entail an opportunity to enter the packaging market because of these ICs' higher price point and need for new packaging technology. An increase in US ATP firms could also directly benefit the DoD by creating highly customized and secure SoC or SiP ICs constructed using less-sophisticated ICs, thus allowing the DoD to gain the benefits of customized near-leading-edge capability without also bearing the full burden of the concomitant investment.

#### Design

Although the most sophisticated ICs are fabricated overseas, more than half are based on US designs, helping US firms meet current demand and lending resilience to the US market. Flaws, bugs, or back doors introduced during design could be difficult to detect through V&V testing, but US-developed designs

Figure 11: Impact assessment of the microelectronics production segments on the US microelectronics ecosystem

|                                | INCREASING IMPACT                                  |                                                   |                                                      |                                                    |  |

|--------------------------------|----------------------------------------------------|---------------------------------------------------|------------------------------------------------------|----------------------------------------------------|--|

| SEGMENT                        | RESILIENCE TO US<br>CUSTOMERS/USERS                | ASSURANCE TO US CUSTOMERS/USERS                   | US ALIGNMENT WITH<br>TODAY'S DEMAND                  | US ABILITY TO ADD VALUE                            |  |

| Fabrication                    | Small-node foundries concentrated in East Asia     | Many backdoors can be detected by US V&V          | US fabs competitive in narrow areas of market        | New designs could command premium price            |  |

| Packaging                      | Most, but not all, ATP and OSAT firms in East Asia | Minimal undetectable backdoor opportunities       | US not competitive due to labor and regulatory costs | US ATP for SoC, 3D, etc. could warrant higher cost |  |

| Design (Core IP)               | US leads in number/<br>sophistication              | Vulnerabilities can be hidden, but most IP is US  | Strong demand for current, emerging US designs       | US could exploit lead in core IP for new designs   |  |

| Design tools                   | US supplies essentially al design tools            | Malware could enable back doors; but tools are US | US design tools used throughout industry             | US tools remain essential for exploiting new tech  |  |

| Manufacturing<br>Equipment     | US or allies supply nearly all high-end equipment  | Undetectable vulnerabilities unlikely             | US and European equipment predominant                | Break from smaller nodes could grow US value add   |  |

| Validation<br>and verification | Largely done overseas, but oversight is strong     | Poor V&V could miss bugs, etc., but is US-based   | US does not provide substantial portion              | New designs could justify higher US costs          |  |

The framework can assess the impact of each production segment on US microelectronics supply resilience and assurance, and the ability of the US microelectronics industry to contribute to current and future demand.

Source: Authors

could reduce the likelihood of such potential vulnerabilities being introduced into products intended for US customers. US leadership in core intellectual property like x86 or Power PC architectures would also position US firms to be able to contribute to long-term future technologies, which would derive much of their value from core IP. As computing architectures increase in heterogeneity and move away from standardized core IP models, opportunities are growing for novel designs and for IP specialized to support certain forms of processing, like signal processing that can benefit more from software-hardware co-design than from decreasing node size.

# Design Tools

Similar to IC designs and core IP, the dominant market position of US-developed EDA tools increases the resilience and assurance of the microelectronics supply chain for US customers. They also play an essential role in the design of more than 80 percent of the chips sold to satisfy current demand, and EDA tools will play a central role in adding value to future chip technologies. As technologies like 3D packaging and increasingly heterogeneous SoCs mature, new design tools will be needed, providing a unique opportunity to expand the US lead in this area.

# Manufacturing Equipment

US-built equipment manufactures half of the ICs produced today, fostering ecosystem resilience and supporting current customer requirements. Because undetectable flaws, bugs, and back doors are unlikely to be introduced through manufacturing equipment, the prevalence of US-made manufacturing equipment does not substantially improve assurance. In addition, US companies do not build the EUV equipment needed to continue shrinking node size and so increasing IC density along the current S-curve. However, US equipment suppliers could exploit their strong overall market position to more easily implement new near-term and long-term future IC designs that do not rely solely on shrinking node size to advance technologically.

#### Validation and Verification

ATP firms test ICs as part of the assembly and packaging process but may not fully validate that ICs are constructed as designed or verify that they will perform as intended under all realistic conditions. For this reason, V&V is usually the responsibility of the organization that receives the finished IC and that often also designed it. V&V and oversight of the IC manufacturing process by US-based customers or IDMs increases ecosystem resilience, but compromised or insufficient V&V could significantly degrade assurance. US firms do not contribute substantially to ATP, but their oversight and V&V capabilities could be leveraged to add value in future IC technologies, supported by the DoD's efforts to develop zero-trust models of microelectronics integration. 68

# **Evaluating Potential Solutions**

The assessment framework described above suggests opportunities for US government policies and investment to improve the resilience, assurance, and competitiveness of US microelectronics. For example, the current lack of diversity in fabrication undermines resilience and assurance, but US foundries may not be competitive building today's leading-edge chips unless they receive financial support and leverage foreign expertise. This approach may be a bridge to future domestic fabrication facilities that could command higher prices by exploiting US strengths in core IP, EDA tools, and manufacturing equipment to move up the value chain and produce near-and long-term microelectronics technologies. This and other initiatives currently being considered are summarized in Figure 12 and assessed in the following paragraphs.

# Support Operations of US Leading-Edge Node Fabrication and ATP facilities

Diversifying fabrication would improve microelectronics resilience and offer alternatives when an incumbent supplier's assurance is in doubt. However, US fabrication plants would likely not be cost-competitive in producing the most advanced chips against overseas facilities that have built competence in the newest manufacturing techniques, and which enjoy

Figure 12: Impact assessment of supply chain-strengthening proposals using the four-factor framework

|                                                                                                   |                           | INCREASING IMPACT OF INITIATIVE               |                                               |                                                  |                                                        |

|---------------------------------------------------------------------------------------------------|---------------------------|-----------------------------------------------|-----------------------------------------------|--------------------------------------------------|--------------------------------------------------------|

| INITIATIVE                                                                                        | COST                      | RESILIENCE TO US CUSTOMERS/USERS              | ASSURANCE TO US CUSTOMERS/USERS               | US ALIGNMENT WITH<br>TODAY'S DEMAND              | US ABILITY TO ADD VALUE                                |

| Fund operation of US leading-edge node fabrication and ATP by US or US/foreign partnership        | \$1-5<br>Billion/<br>year | <5nm ICs could be replaced by new designs     | Modestly improved oversight in US             | Will meet some<br>demand but lag<br>leading edge | US can leverage fab for design, core IP insights       |

| Incentivize larger node<br>fabrication in US or<br>ally via tech transfer,<br>purchase agreements | \$5+<br>Billion           | Lower-end ICs more vulnerable to shocks       | Modestly improved oversight in US/ally        | Will meet demand at risk of overcapacity         | US can leverage fab<br>for design, core IP<br>insights |

| Stand up US public-<br>private investment<br>partnership for maturing<br>near-term future tech    | \$5+<br>Billion           | New designs may be cost effective in US/      | Near-term tech could offer greater security   | Maturing tech weakly aligned with demand         | US can exploit talent, design, IP, equipment           |

| Accelerate "zero trust"<br>and architectural<br>approaches to provide<br>assurance                | \$1<br>Billion            | US could perform more segments of value chain | Could obviate many vulnerability concerns     | V&V rapidly growing; could be disrupted          | US exploit talent,<br>design, IP, and<br>customer base |

| Customer coalition<br>with export/import/tariff<br>guarantees                                     | \$<1<br>Billion           | Compel suppliers to diversify geographically  | Pressure on suppliers could improve oversight | Could increase US competitiveness v.             | Could build customer base for future tech              |

| Fund research and prototyping of "new S-curve" technologies                                       | \$5+<br>Billion           | US could establish role in fab, ATP, V&V      | Heterogeneity can improve security            | Long-term tech weakly aligned with demand        | US exploit talent,<br>design, IP, and<br>customer base |

Source: Authors

government subsidies, tax incentives, and lower labor costs relative to the United States.<sup>69</sup>

US foundries and ATP facilities could produce leading-edge chips at a competitive price if they received government support to partially offset higher labor and compliance costs compared to overseas competitors. US-based Intel is attempting this course of action today. Intel's initiative shows that corporate R&D funding is available to at least partially fund construction of new high-end semiconductor production capacity. The US government's support to leading-edge fabrication could therefore be less than private investment and center on tax or regulatory relief that would help foundries remain competitive once they are in operation. Ongoing support would also improve the business case for new US foundries, which will make them more attractive for corporate or other private capital that expects investments to begin paying off within about 5 years.

The US government could build on the establishment of domestic leading-edge fabrication capacity by devoting most of its microelectronics funding to sponsoring development of fabrication and advanced packaging capabilities for near- or long-term future chip architectures. These technologies depend on high-end fabrication capabilities and are not attractive for corporate R&D funding due to their distant return on investment. Government financing could catalyze the US microelectronics industry's movement up the value chain into new technologies where it could gain a greater market share of production segments outside existing US strengths in EDA tools, core IP, or manufacturing equipment.